1 概述

ANSYS Totem是晶體管級電源可靠性、噪聲和可靠性仿真平臺,該平臺可以使您的IP、模擬、混合信號設計和全定制數字設計滿足越來越嚴格的電源完整性及可靠性要求。Totem具有SPICE級別的分析精度,并支持在分析時納入封裝以及襯底寄生。

? 完整的解決方案

Totem支持用于模擬、LEF / DEF(用于數字)的主要數據格式(GDS,OASIS,LVS數據庫等),并且與主要的spice仿真環境兼容。它具有處理非常大的設計的能力,并具有出色的宏建模功能,可以為SOC signoff生成準確而緊湊的IP模型。

? 一流的Signoff Analysis

Totem的提取、模擬、電遷移和自熱分析核心引擎均通過了主要技術節點的認證,并多次與Spice和硅測量結果進行了關聯。Totem已通過多家主要鑄造廠的認證,并且是多家主要半導體公司的首選signoff工具。

? 廣泛的設計范圍

Totem提供了涵蓋從早期到signoff的全面分析套件。它可以有效地處理各種設計風格,例如SerDes,數據轉換器,電源管理IC,嵌入式存儲器,DRAM,閃存,FPGA和芯片圖像傳感器。此外,它還提供多種分析功能,包括基板噪聲分析,RDSON分析,熱和ESD分析,以應對不同設計中的挑戰。它還為客戶提供了一個可配置的座艙,可根據工作流程自定義其分析。

2 功能特點

? 經硅驗證的模擬及混合信號EM/IR設計signoff

Totem靜態分析可幫助您驗證IP及全芯片設計的電源地網絡的魯棒性。動態電壓降分析可暴露因局部晶體管同時開關而導致的設計缺陷,并可反映實際的電路操作以及因此引起的包括變化的電流需求,及其與電源網絡的電容及電感寄生的相互影響——可能導致電源電壓下降或接地電位反彈。

Totem可以分析從系統/PCB到片上電源地及襯底的整個電源地分配網絡上的噪聲傳播。多個客戶對硅實測值和Totem的仿真結果進行過驗證并高度認可,這充分證明了Totem的精確度。硅實測和仿真結果驗證包括從IP到全定制芯片,工藝節點也擴展到涵蓋目前先進的技術節點,包括7nm。

Totem是業界優秀的模擬及混合信號電源噪聲完整性及可靠性設計交付解決方案,所有的大型半導體公司在生產流程中都會使用,這無疑是對Totem精確度的進一步認可。

? 早期和設計中分析

在模擬和混合信號設計中,通常認為EM和IR分析盡可能接近錄音帶。這是由于傳統工作流程的基本局限性所致,要求設計必須保持LVS干凈以執行提取,仿真并獲得可靠的EMIR結果。但是,隨著設計周期的縮短,在設計過程的早期階段就越來越需要進行設計內分析。這是由于技術的擴展,導致更薄的互連表現出更高的寄生電阻,更低的EM容限,更高的功率密度和更低的工作電壓。

Totem提供了各種功能,例如電網缺陷分析,缺少通孔,P2P檢查以及各種早期的靜態和動態IR和EM分析,這些功能可以突出設計缺陷,而這些缺陷的成本很高,難以解決貼片問題。這些內容以直觀和用戶友好的方式呈現給設計人員,使他們可以做出關鍵的設計決策,例如電網規劃,凸塊放置,去耦電容帽優化,關鍵網絡上的EM等。

? 電源管理芯片的分析

移動及IoT設備的爆炸性增長以及這些設備對能耗效率要求的提高推動了對電源管理IP的需求。任何可能導致局部電流密度增加、電壓下降或噪聲耦合的設計缺陷都會影響電力配送。因此,設計人員必須找出此類缺陷,尤其是特定于電源管理電路的缺陷。因為電源管理IP廣泛應用于全芯片集成的多種功能模塊,設計人員必須在全芯片設計的背景下看待這些缺陷,這無疑更具挑戰。

Totem是適用于全芯片模擬、混合信號I/O設計的電壓降、可靠性(EM/ESD)及噪聲耦合分析的綜合性仿真平臺。同時針對電源管理芯片,Totem可以對電阻、電流密度及保護環這些重要項目進行分析,確定設計缺陷。此類驗證既可以在PMIC模塊或IP的設計階段完成,也可以在全芯片頂層級別的集成階段完成。

? Signoff分析

選擇正確的矢量來給電網施加壓力是一個挑戰,因此設計人員可能經常會運行更長的仿真來涵蓋更多場景。在整體模擬中包括電網復雜性會大大增加傳統流程的分析時間,而傳統流程耗時數天至數周。這使得任何ECO更改都變得不可能,并可能導致昂貴的金屬重制,甚至導致硅產量問題。

Totem提供了多種選項,可以對大型混合信號設計進行準確的簽核。諸如布局和路線數字數據庫的本地處理以及復雜AMS的層次分析之類的關鍵功能通過促進自下而上的匯總視圖,極大地簡化了總體流程,在該匯總視圖中,塊所有者可以對其塊進行全面驗證并匯總一個全面的多狀態晶體管頂級分析的抽象級別或抽象宏模型。在將幾個模塊與數字位置和路線數據集成在一起的同時,仿真可以利用并對齊子模塊的不同功能狀態,以模擬幾種可能給電網帶來壓力的最壞情況。

復雜混合信號接口的經典示例是PHY接口。串行接口(又名SerDes)可以分為定義明確的子塊,如時鐘和數據片。可以將它們分析并建模為宏模型。這些宏模型可以保留完整的,未降低的電網,直至器件擴散,以及詳細的多狀態電流曲線,為不同的功能狀態建模。此外,接口中的任何數字模塊都可以使用向量(VCD / FSDB)或無向量的方法進行詳細建模,直至標準單元級別。完整的IP級別分析需要將這些時鐘和數據切片視圖結合起來,并包括封裝模型以執行詳細的瞬態電壓降分析。Totem分析了噪聲在整個功率傳輸網絡中的傳播情況,從封裝到芯片上電網和基板網絡,整個功率傳輸網絡都在傳播。

? 高速千兆SerDes IP分析

由于高速SerDes的性質,抖動(影響錯誤率)、功率(影響每比特能量)以及可靠性(影響集成電路的長期操作)是設計師經常面臨的挑戰。使用先進的制程技術導致電流密度增加,同時結合熱的因素會極大地影響電源完整性以及 EM可靠性問題,這進一步增加了設計障礙難度。為了盡可能降低故障風險,必須對SerDes IP從內部每個單獨模塊到整個IP針對電源噪聲以及可靠性問題做檢查。

Totem提供一個綜合性的仿真框架,適用于模擬、混合信號 I/O 設計的電壓降、襯底噪聲、可靠性(EM/ESD)及噪聲耦合分析。此外,Totem可生成SerDes IP電源模型用于頂層設計分析,以實現全覆蓋的芯片壓降、電遷移以及ESD完整性分析。這些模型增加了SerDes在全芯片級分析時的功耗特征可信度和覆蓋率。

? 襯底噪聲分析

電路中常見的是來自于高速數字電路的噪聲到敏感的模擬及RF塊的噪聲耦合。這需要展開真正的模數混合電源噪聲及可靠性分析。

Totem具有晶圓代工廠確認的具有成功流片案例追蹤記錄,用于襯底噪聲分析簽核的混合信號EM/IR工具,它可以幫助您進行噪聲時域、頻域分析及評估保護環質量的影響,從而加快設計交付。

NXP利用此功能將多個無線電集成到單個芯片上,同時盡可能地降低了來自片上高速數字信號的襯底噪聲。他們的分析結果也與實際硅片結果匹配的很好。

? 高級調試

根本原因分析以及假設性修復是任何分析工具都應具備的重要功能,尤其是關注降低噪聲容限、增加熱效應并盡可能減少封裝及PCB寄生效應的電源噪聲完整性及可靠性解決方案。在包含數字、模擬及RF信號的混合信號芯片上,復雜性更為突出。

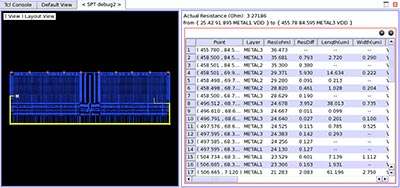

Totem基于布局的分析以及內置圖形化界面通過將仿真結果疊于布局之上,全面直觀地顯示故障原因,這便于您快速展開交互式根本原因分析以及假設性修復,進而顯著縮短調試周期。

Totem的通用、多功能圖形化界面的外觀和感覺類似于版圖編輯器,并通過精密的多選項卡、多窗格功能提供對仿真結果的完全可視性。

? IP signoff及SoC集成

IP是每個SoC設計中不可或缺的一部分。無處不在的連接性需求已經推動SoC中的集成程度甚至已經超越摩爾定律的預測范圍。IP不僅需要在獨立模式下工作,還需要同其他第三方IP一起集成于目標SoC之后的復雜電路環境中工作。IP集成及驗證被視為SoC設計師面臨的幾個嚴峻的挑戰。芯片頂層壓降分析時,同一IP在兩種不同的工作模式下操作,電壓降可能迥然不同。為確保IP在SoC中電源完整性,設計師必須精確建模并描述IP在不同操作模式下的特性用于頂層電壓降分析。將IP移交給SoC團隊時,提交的數據也必須包括IP的電氣及物理屬性,以及電源完整性簽核限制參數等信息。

? 先進的可靠性分析

盡管FinFET在面積,性能方面具有多個優勢,但FinFET設計上的局部熱梯度可以達到器件上高達30攝氏度的溫度,這主要歸因于FinFET超薄,高電阻互連的3D特性以及導熱性差的電介質。Totem提供了全面的EM signoff,包括電源/信號EM分析,建模焦耳加熱,FinFET的導線耦合和自熱以及它們對互連的影響。主要代工廠均已啟用該流程,進行FinFET設計的客戶均使用該流程。Totem還啟用了統計EM預算編制功能,可以滿足汽車和其他關鍵任務應用程序的需求。

首頁 > 產品中心 > 半導體仿真

首頁 > 產品中心 > 半導體仿真