1、 文檔目標

對 JTAG 接口有更多的認識,在遇到關于 JTAG 接口問題時有一些排查的思路。

2、 問題場景

在使用調試器過程時,免不了要接觸到 JTAG 接口,當出現連接不上時,就不知道從哪來進行排查。

3、軟硬件環境

1 )、軟件版本:不涉及

2 )、電腦環境:不涉及

4、JTAG 接口介紹

1. JTAG 接口定義

JTAG(Joint Test Action Group,聯合測試工作組),是一種國際標準測試協議,用于芯片內部測試。

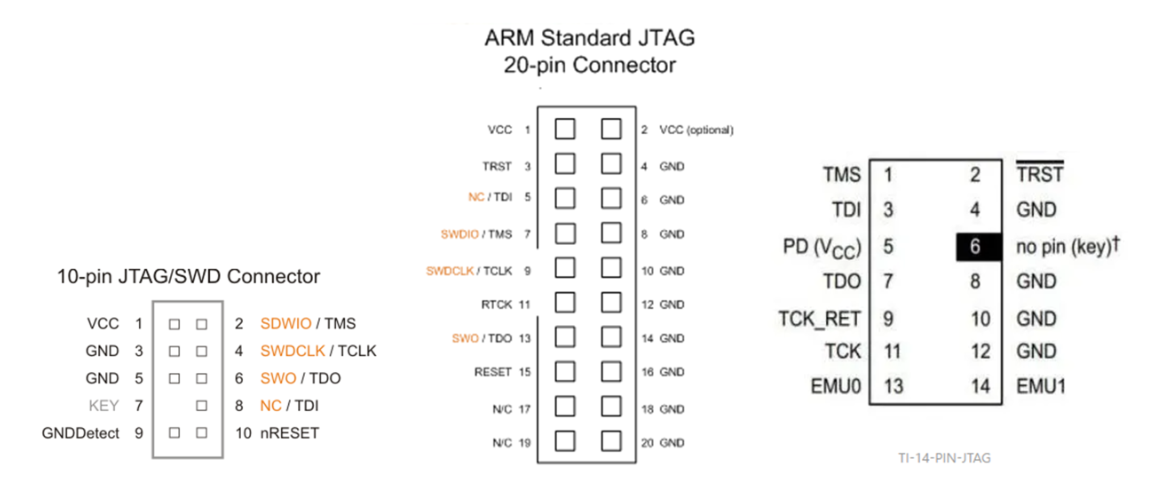

標準的JTAG接口是4線:TMS模式選擇、TCK時鐘、TDI數據輸入、TDO數據輸出。

也包括一些測試復位,電源,地等。

2. JTAG 接口的 10PIN 20PIN 14PIN

3. JTAG 接口作用

JTAG 接口的主要作用有三個,

a. 下載,即把程序下載到芯片的 flash 里或者外部存儲器里。

b. 調試,實時調試程序的運行,控制程序全速執行,單步,斷點等。

c. 邊界掃描,獲取芯片內部的信號邏輯狀態及芯片引腳的狀態。

4. JTAG 接口復用

在某些芯片上 JTAG 口和其他 GPIO 是復用的,就是在最開始燒寫程序,之后就可以在程序運行的時候占用這個管腳,通常不會這么做,只有考慮成本用更少的芯片引腳時才這樣做。

需要在燒寫程序的時候保證芯片在復位狀態下,然后才能正確識別 JTAG。

5. JTAG 接口問題與排查

1)、在使用 JTAG 調試時,首先要排查的是硬件的連接和供電問題。

例如找不到目標板:

//alidocs.dingtalk.com/i/nodes/ZgpG2NdyVXrKBv1YTRqRwqp48MwvDqPk?doc_type=wiki_doc#

2)、另外還有一種是對于實物接口的線序不清楚,如圖 1 ,通常這種排線,紅線為 1 腳,同時在座上可以看到一個倒三角標記,也表示是 1 腳。

圖 1

如圖 1 ,通常這種排線,紅線為 1 腳,同時在座上可以看到一個倒三角標記,也表示是 1 腳。

圖 2

如圖 2 ,通常這種排座,也可以看到一個倒三角標記,表示是 1 腳。確定了 1 腳位置之后,再排查接口的線序是不是正確。

3)、再有就是關于接口的上下拉問題。

圖 3

通常是不需要對 JTAG 口進行上拉或下拉的,某些仿真器為了保證初始狀態的確定性會有一些要求,一般參考圖 3。

6. 其他調試接口

a. SWD

串行調試(Serial Wire Debug),需要4個SWDIO和SWCLK 及電源和地(或者5個,增加 SWO)引腳。

SWDIO(Serial Wire Debug Input/Output)是SWD接口中最重要的線之一。它既是數據線,也是控制線。在調試過程中,SWDIO用于傳輸調試信息和數據,同時還負責傳輸控制信號。

SWCLK(Serial Wire Debug Clock)是SWD接口中的時鐘線,用于同步SWDIO線上的數據傳輸。

SWO(Serial Wire Output)是SWD接口中的輸出線,用于將處理器內部的跟蹤信息輸出到外部調試器。

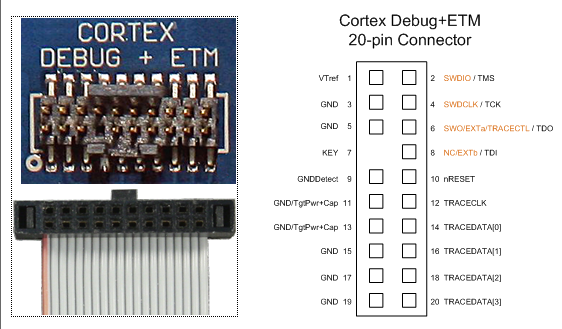

b. Cortex Debug+ETM

ETM指令跟蹤。(TRACEDATA[0..3])上輸出數據,(TRACECLK)用于跟蹤時鐘。

首頁 > 資源中心 > FAQ

首頁 > 資源中心 > FAQ